服务商:阿昆谈DFM

¥2000

请详细描述您开发案例,请勿在案例或图片里写联系方式,案例不符合规范的,审核不会通过的。

开发案例样本

1、工作背景;

15年生产工作经验,从事过生产装配\电子元件的来料检验\器件物料选型与代替\PCB的设计评审\产品设计项目\熟悉SMT加工与PCB制造

2、开发经历,做哪些项目;

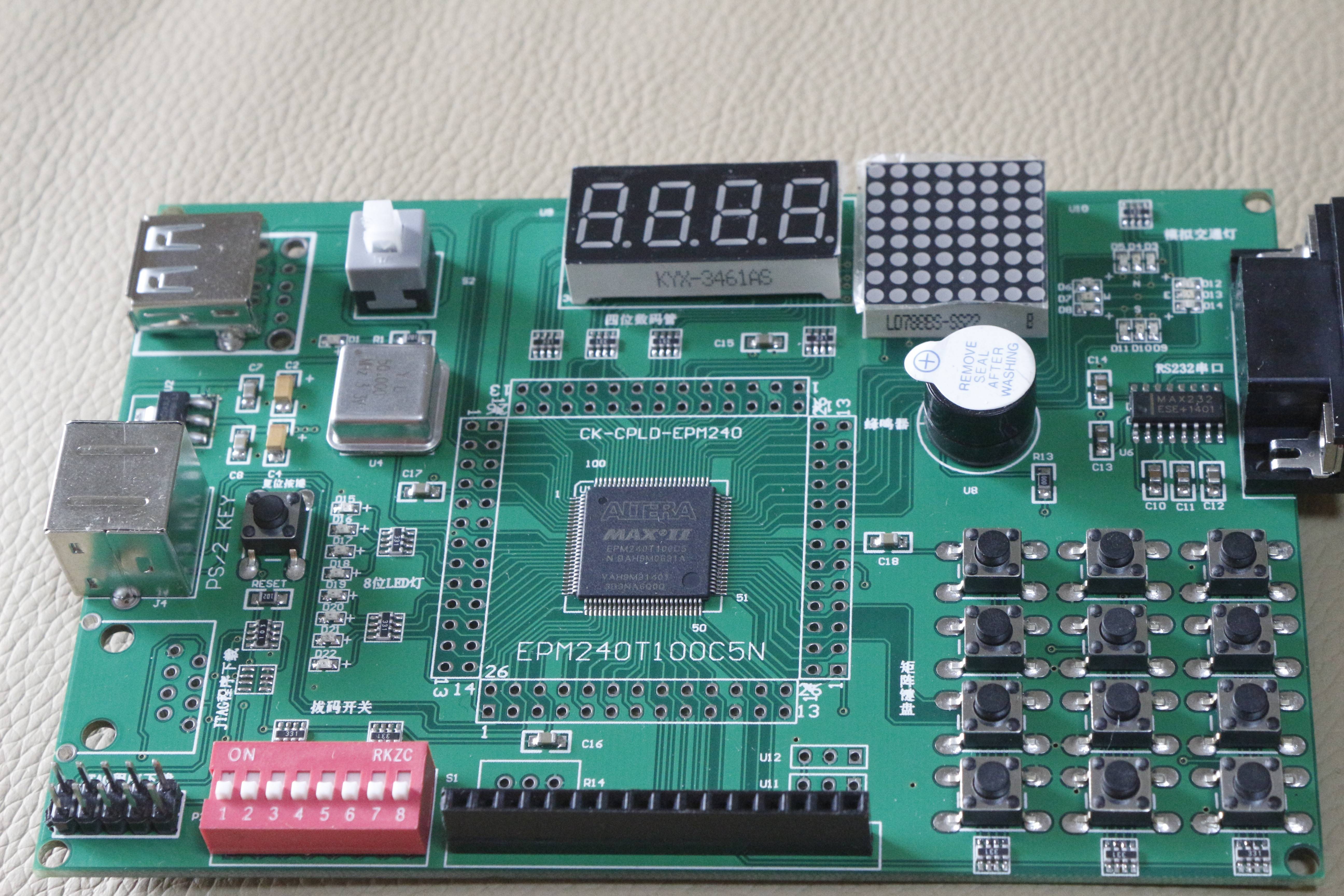

VGA分配器、CPLD开发板等

CK-EPM240学习板件是基于EPM240T100C5N的FPGA/CPLD学习开发平台。提供了丰富的硬件资源和大量的实验例程,并详细介绍了如何在本实验平台上完成各个实验过程,实现对板上资源的利用,从而使用户对数字系统的开发流程熟练掌握。用户无需再购买任何开发工具,只要有一台计算机,就可以学习开发FPGA/CPLD了;同时引出EPM240的所有I/O口可全部用于扩展,方便用户开发自己的产品,最大限度的为用户节约成本和加快学习开发速度。

主芯片采用ALTERA MAXII系列的EPM240T100C5N(相当于8650门CPLD,容量是以前的EPM7128的两倍,并且可以烧写至少10万次以上)。

在所有CPLD系列中单位I/O成本最低,功耗最低。

MAX II运用了低功耗的工艺技术,和前一代MAX器件相比,成本降低了一半,功率降至十分之一,容量增加了四倍,性能增加了两倍。

逻辑单元(LE):240个

典型等效宏单元:192个

最大用户IO脚:80个

速度等级:5ns

注:CPLD和FPGA可以看成一类器件(CPLD适合做组合逻辑电路,FPGA适合时序电路),编程语言,操作方法、软件一样,但CPLD成本更低,更适合初学者学习硬件编程言,所以初学者不要纠结用哪一个,其实学习方法都是一样,选者简单的,成本低的才最合适。

相反,价格高,功能复杂的反而不是适合初学,太复杂,容易让初学产生恐惧。